20位嘉宾演讲内容剧透,架构创新专场超强阵容揭晓!年度AI芯片盛会邀您下月见

演讲主题:《Chiplet迈向大芯片:计算、存储与互联》

内容概要:本演讲将从大芯片需求出发,探讨大模型、自动驾驶、机器人等对芯片的需求,继而从计算、带宽供给和互联三个方向讨论Chiplet相关的解决方案。

2、壁仞科技副总裁兼AI软件首席架构师 丁云帆

演讲主题:《国产GPU如何系统性的解决大模型算力难题》

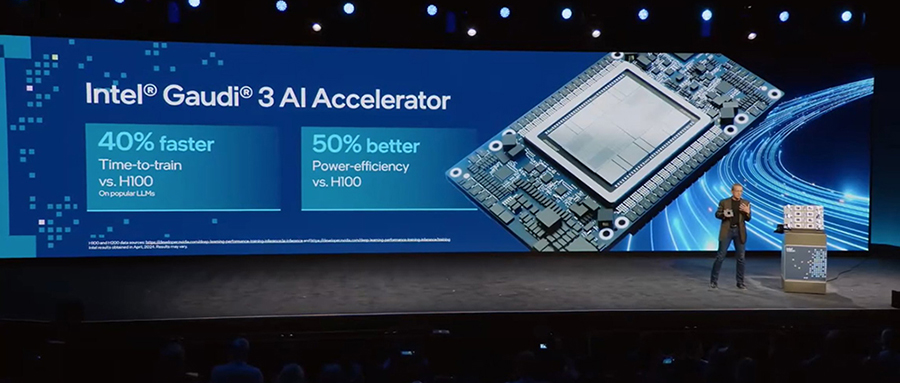

内容概要:以ChatGPT为代表的大模型技术引发了新一轮的科技革命,国内外呈现了百模争艳的状态,并且已经开始了广泛的应用落地。大模型的训练和落地带来了巨大的算力需求,以LLaMA3 千亿参数为例,Meta建设了18000个H100的集群来满足训练需求。目前国内存在着较大的算力供应瓶颈,这也给国产AI芯片带来了巨大机遇,国产千卡集群在逐步落地应用。大模型训练是一个系统工程,需要软硬件协同,算法与工程协同,对计算机体系结构如计算、存储、通信都带来了巨大挑战,另外千卡集群对并行扩展、稳定可靠、弹性伸缩提出了更高的要求,同时不同异构GPU集群形成了算力孤岛,如何实现异构GPU协同训练通过算力聚合共同训练大模型非常关键。针对上述挑战,壁仞科技基于其高性能国产GPU打造了软硬一体、全栈优化、异构协同、开源开放的大模型整体解决方案。

本次演讲将从硬件集群算力、软件有效算力、异构聚合算力三个维度分享壁仞科技如何系统性的解决大模型算力难题。

3、中昊芯英创始人、CEO 杨龚轶凡

演讲主题:《从GPU到TPU,AI大模型基础设施的变迁与未来》

内容概要:每一次历史性的科技浪潮中,底层基础设施的革新总是扮演着至关重要的角色。市场容量巨大的应用领域,其计算芯片硬件体系架构往往呈现出从通用型逐渐演变为专用型的历史规律。如今,随着大模型计算需求和复杂度的指数级增长,传统GPU在用于大模型训练时的成本高、算力利用率低、能耗大的瓶颈开始显现。全球科技巨头如微软、AWS、特斯拉和OpenAI,以及新兴的明星初创企业如Groq和Etched,都在探索研发AI专用芯片以替代英伟达GPU;7月底,苹果公司也宣布使用谷歌TPU(张量处理器)而非英伟达GPU来训练其AI模型。全球AI领域,正发生着使用非GPU架构来构建更高效的大模型基础设施的转向。

TPU是谷歌专为加速机器学习和深度学习任务而设计的专用芯片,专注于大模型训练和推理中常用的张量运算。在此次演讲中,曾在谷歌 TPU 核心研发团队深度参与过 TPU v2/3/4 的设计与研发工作的杨龚轶凡,将分享AI算力硬件的进化历史与趋势,TPU与GPU的关键差异及用于大模型训练时的优势,以及中昊芯英自研的国内首枚且唯一已量产的全国产自主可控TPU 架构AI芯片如何重塑AI大模型算力基础设施。

4、芯和半导体技术市场总监 黄晓波

演讲主题:《EDA使能AGI时代大算力芯片Chiplet集成系统开发》

内容概要:人工智能与算力设施等新质生产力重塑行业数字化转型,同时人工智能对算力的需求永无止境,高性能计算芯片采用Chiplet技术已成为后摩尔时代的行业共识,有力突破了半导体晶圆先进制程工艺带来的芯片PPA提升瓶颈。Chiplet集成系统面临架构探索、顶层规划、物理实现、多物理场分析、系统验证等一系列挑战,构建针对Chiplet集成系统的设计流程与EDA平台是Chiplet产品落地的首要考虑。

本次分享将聚焦当前大算力芯片Chiplet设计的典型应用,结合实际案例阐述Chiplet新的设计流程与多物理场仿真EDA方案,解决信号完整性、电源完整性、热及应力等方面的问题,助力用户加速Chiplet集成系统的开发与优化。

5、苹芯科技CEO 杨越

演讲主题:《存算的进阶——从神经网络到大模型》

内容概要:存算一体技术正在深度参与AI芯片的设计与落地。基于静态随机存储器SRAM的存算一体芯片已经在AI 1.0领域内开启了落地之旅,凭借突破性的高能效比,这类芯片给予了端侧电子产品前所未有的AI能力。另一方面,随着大模型技术的成熟与应用推广, 内存带宽瓶颈和计算能效问题显现。我们从存算一体技术视角分析大模型加速芯片的解决方法和架构设计特点,为降低推理延迟、提高能源效率、实现更高的并行计算能力提供一个新的思路。

此次演讲将深入分析如何以存算一体技术为基础,构建高效加速AI计算与大模型计算的芯片架构。以及如何通过这一技术突破,使存算一体芯片在大模型时代成为关键的推动力量,为未来AI应用的发展提供崭新的机遇和路径。

6、珠海芯动力创始人兼CEO 李原

演讲主题:《面向边缘端大语言模型的RPP架构芯片与落地实践》

内容概要:AI PC作为未来的发展趋势,正引领着技术创新的潮流,而大语言模型在边缘端的部署更是这一趋势中的重要一环。

为了实现大语言模型在边缘端的稳定、高效运行,我们需要精心规划技术路径和部署策略。芯动力将深入剖析这一过程中的关键要素,分享其在硬件加速技术方面的独到见解。通过针对大语言模型的计算特性进行数据流的优化,以可重构并行处理器的方式,来高效灵活的处理边缘端大模型的流畅运行。

然而,在这个领域也面临着一些挑战。模型规模不足和功耗过高都可能影响边缘端设备的性能和用户体验。因此,寻找一种能够最好地支持大语言模型、适合其落地的芯片或架构显得尤为重要。

为此,芯动力分析了大语言模型在RPP架构中如何支持高效计算,与传统GPGPU架构相比,它同时实现了灵活的通用计算,并在低功耗与高效率方面显著提升。同时,针对大语言模型的稀疏化特性进行了优化,进一步提升了内存利用率和访存效率,降低了功耗,从而延长了边缘端设备的续航时间。这一创新方案为解决当前面临的挑战提供了新的思路和方向。

7、锋行致远创始人兼CEO 孙唐

演讲主题:《存算大模型加速系统》

内容概要:存算一体技术能高效提升AI业务算效比,目前大模型底层架构技术演进迅速,国内芯片到软件技术都遇到挑战,目前存算一体技术对于大模型应用系统具有较好的加速协同能力。

本次演讲,将分享锋行致远存算一体芯片对相关场景加速应用能力和技术细节。

8、PhySim资深产品工程师 黄建伟

演讲主题:《Chiplet先进封装中的多物理场仿真解决方案》

内容概要:随摩尔定律逼近物理极限,后摩尔时代下的异构集成(Heterogeneous Integration)芯片技术——“芯粒”(Chiplet )应运而生,将一个功能丰富且面积较大的芯片拆分成多个芯粒,并将这些由不同工艺生产的芯粒通过MCM、2.5D、3D等先进封装技术组合形成一个系统芯片。通过Chiplet技术,可以显著提升芯片设计的灵活性及工艺良率,降低设计难度与制造成本。

但随着先进封装中芯片堆叠数量与互连密度的增加,芯片的发热问题变得愈加严重、散热也更加困难。如果不能较好地解决发热与散热问题,芯片内部累积的焦耳热则会对其性能造成影响,还可能会带来较高的热应力风险。

除此之外,由于信号速率的提升,信号通道对高速信号的影响也不容忽视,其中损耗、反射以及信号间的串扰等问题尤为突出。

PhySim自主研发的的多物理场仿真平台可以对先进封装中的多物理场问题进行高性能仿真,其中ACEM、TurboT-BCA、PhySim-ET分别可以解决三维全波电磁仿真、电子散热仿真、电热协同仿真问题,帮助用户在产品实体化前进行有效的仿真验证,规避潜在设计风险。

本次演讲将会分享以下几个关键点:

1.异构集成芯片技术(Chiplet)的兴起:随着摩尔定律逼近物理极限,异构集成技术应运而生,将大芯片拆分为多个芯粒,并通过先进封装技术组合成系统芯片,提升设计灵活性和良率,降低制造成本。

2.芯片发热与散热问题:随着芯片堆叠数量与互连密度的增加,发热问题加剧,散热困难,可能影响芯片性能和带来热应力风险。

3.信号通道问题:信号速率的提升导致损耗、反射和信号间串扰等信号通道问题突出。

4.仿真平台的意义:有效仿真验证可在产品实体化前规避潜在风险,提高产品设计效率和成功率。

5.多物理场仿真平台的应用:PhySim自主研发的仿真平台可对先进封装中的多物理场问题进行高性能仿真,包括三维全波电磁仿真、电子散热仿真、电热协同仿真等,帮助规避潜在设计风险。

9、安谋科技产品总监 杨磊

演讲主题:《端侧AI应用“芯”机遇,NPU加速终端算力升级》

内容概要:随着AI大模型持续向边缘侧和端侧渗透,AI计算和推理工作正逐步由云端迁移至手机、PC、汽车等智能终端产品上运行,在这一过程中,NPU(神经网络处理器)能够以其更简单的控制流、更高的效率以及更低的功耗处理AI工作负载,特别是在视觉、语音及自动驾驶等高度依赖实时性的应用场景中表现出色。

本次演讲将分享端侧大模型应用的前沿趋势以及安谋科技自研NPU处理器的最新进展,共同探索如何为AI、物联网、智能汽车等新兴领域不断迭代的计算需求提供更为全面和高效的解决方案。

10、聆思科技副总裁 徐燕松

演讲主题:《大模型时代,算法算力一体化芯片的思考与布局》

内容概要:在大模型时代,技术发展给各行各业带来了全新的产业机遇,甚至不亚于互联网、手机带来的行业变革。在这个时代的风口,算法算力一体化对于智能硬件的发展具有极其重要的意义。这种一体化不仅涉及芯片算力与算法资源的紧密结合,还包含了整个嵌入式开发生态的建设,以此减少终端设备在智能化开发过程中大量的重复造轮子的工作,大幅提高研发效率以及性价比。通过这种软硬件深度结合的方式,在性能和成本之间找到更优的平衡点,加速了技术的创新和应用普及,进一步推动了整个行业的前进步伐。

本次演讲将从大模型时代硬件需求特点、算法算力一体化芯片的技术与架构、以及行业实际应用案例分析,全面诠释聆思科技在算法算力一体化芯片领域的思考与布局。

11、富瀚微资深市场总监 冯晓光

演讲主题:《边缘视频AI芯片复盘与展望》

内容概要:边缘视频AI芯片,这种专为边缘设备如摄像头和录像机设计的智能芯片,正成为视频内容分析和处理领域的革命性力量。它们在智能安防、交通监控、工业自动化、医疗影像分析等多个领域发挥着至关重要的作用。随着技术的不断进步,边缘视频AI芯片已经经历了几代的迭代,每一次演进都带来了性能的飞跃和应用场景的拓展。

本演讲将深入探讨边缘视频AI芯片的发展历程,分析每一代芯片的关键技术和创新点,以及它们是如何推动相关行业的发展。同时,我们也将展望未来,探讨边缘视频AI芯片在技术、应用和市场方面的潜在发展趋势,以及它们如何继续引领智能化的浪潮,为各行各业带来更多的可能性和价值。通过这次演讲,我们希望能够为听众提供一个全面的视角,理解边缘视频AI芯片的重要性和它们在未来技术发展中的关键角色。

12、芯动科技IP研发副总裁 高专

报告主题:《量产验证的 UCIe Chiplet IP 加速 HPC 芯片系统设计》

内容概要:本次演讲,将介绍UCIe Chiple技术及其发展背景,并着重讲解芯动科技UCIe Chiplet解决方案的技术特点、优势和应用案例。之后,高专还将深入分析UCIe Chiplet市场的发展现状、面临的挑战和未来趋势。

13、硅芯科技总经理 赵毅

报告主题:《针对先进封装的2.5D/3D IC协同设计仿真EDA工具探讨》

内容概要:采用先进封装的2.5D Chiplet/3D IC堆叠芯片正在带来半导体行业的一次重大升级,有效解决了芯片内存墙、功耗墙、面积墙等设计制造瓶颈。然而,2.5D Chiplet和3D IC无论从物理设计,还是物理仿真验证方面都带来了巨大的挑战,对新一代的堆叠芯片EDA工具更是有全新的需求:无论是在设计环节中处理新的单元结构TSV等(相对传统工具产生EDA特性的质变),还是由于多芯片集成,TSV等带来的布局布线解空间急剧上升(相对传统工具计算复杂度上的巨大量变),甚至由于多Chiplet先进封装带来的超高密度异质异构集成,而导致的高难度热电力磁多物理场仿真。

本次演讲,将深入探讨上述挑战和需求,此外还将分享硅芯科技在Chiplet-Interposer-Package Co-design和Performance-Cost-Testability Co-optimization方面的研究,并介绍Chiplet物理设计(2.5D布局布线)、多物理场仿真(SI,PI,Thermal分析)及针对先进封装Chiplet Multi-die DFT测试等板块的2.5D/3D IC新一代EDA工具。

14、锐杰微董事长 方家恩

报告主题:《Chiplet芯片技术在封装级的相关应用》

内容概要:AI技术赋能千行百业智能化已经成为中国社会数字化转型的有力抓手,互联网+/5G+让位于AI+,持续的算力需求带动高性能芯片快速增长。高性能芯片的算力、内存带宽、功耗指标的全面提升因制程因素而面临挑战。半导体技术进入后摩尔时代,Chiplet芯粒和集成芯片技术成为寻求突破的重要研究方向之一。基于Chiplet技术的集成芯片是硅片级IP重构和复用的新架构,在缩短新产品研发周期、提升产品良率和降低成本方面具有独特优势和潜力。D2D高速互联技术、面向封装设计和组装工艺全流程的封装工艺平台成为推动Chiplet封装技术发展的关键技术。

锐杰微科技作为聚焦Chiplet&高端芯片的OSAT企业,本次演讲将阐述Chiplet产业观点,围绕chiplet主流标准和封装技术路线的应用场景、芯粒互联的封装设计和组装工艺平台的重要节点,分享锐杰微在高性能芯片封装级的应用实践。

15、算能高级副总裁 高鹏

报告主题:《开启算力新纪元—— 基于RISC-V的异构算力探索与展望》

16、跃昉科技研发副总裁 袁博浒

报告主题:《基于RISC-V的边缘AI芯片在能源物联网的应用》

内容概要:目前,RISC-V芯片的应用集中在在工业控制、物联网、智能家居等对算力要求不高的领域,AI实际应用落地较少。基于对能源互联网场景的深刻分析,跃昉科技推出业界首款基于RISC-V架构的高端边缘智能应用处理器NB2,并构建了从芯片到系统的整体解决方案,已成功在能源互联网场景实现商业化应用。

本报告将分享跃昉科技针对能源互联网应用场景的需求分析、解决方案和实践经验以及未来演进方向。

17、芯来科技CEO 彭剑英

报告主题:《RISC-V IP的商业化要素与2.0模式》

内容概要:本次演讲,将对RISC-V生态发展的关键商业化要素进行分析,并深入探讨RISC-V CPU IP 的产业价值、发展趋势与协同创新。

18、赛昉科技NoC首席架构师 葛治国

报告主题:《国产高性能NoC IP助力RISC-V众核计算》

内容概要:一致性片上网络(NoC)IP作为高性能计算领域的核心技术之一,广泛应用于数据中心、专用处理器(DPU)、人工智能(AI)芯片等场景。作为构建高效、安全、可持续AI生态系统的基础,NoC IP提升了系统的整体性能,降低整体能耗,进一步推动了人工智能技术的发展和应用。赛昉科技作为专注高性能RISC-V IP和软件解决方案厂商,始终致力于国产RISC-V CPU IP和一致性片上网络(NoC)IP的自主研发,其一致性NoC IP已成功研发至第二代——昉·星链-700(Starlink-700),专为支撑RISC-V众核的高性能计算而设计,为其提供强劲的内核动力。

本报告将深入探讨赛昉科技Starlink-700的架构和设计理念,包括其设计特性、多样化应用场景以及未来演进方向。

19、澎峰科技创始人&CEO 张先轶

报告主题:《面向RISC-V的大模型推理引擎PerfXLM》

内容概要:本次演讲,将介绍澎峰自研的PerfXLM大模型推理引擎,以及PerfXCloud大模型开发与部署平台,并探讨GenAI算力需求急剧增长背景下,新兴的RISC-V ISA在此领域的移植与优化。

20、兆松科技联合创始人兼CTO 伍华林

报告主题:《面向RISC-V异构AI芯片的“大编译器”设计和实现》

内容概要:如何快速适配各类AI框架,支持各类模型高效的运行,以及让用户轻松编写高性能的算子库,成为一款AI芯片能否得到市场认可的必要条件。 同时,进一步降低AI芯片的软件栈研发成本和算子库维护成本,提升硬件利用率,也成为AI芯片公司走向盈利的必经之路。

兆松科技为解决AI芯片软件栈和算子库的性能和维护等难题,提出了“大编译器”的概念。传统编译器只针对某一特定指令集的芯片产生单线程或者多线程的可执行文件,兆松科技基于MLIR框架设计的“大编译器”,支持PyTorch, Tensorflow, ONNX, JAX导入,结合Triton和Mojo(未来支持)等类Python语言编写的高层次算子库,在统一的MLIR多层中间方言实现全局的图优化以及更优的算子融合策略,从而进一步提升AI芯片的效率。同时,“大编译器”还对平台相关的runtime进行了平台无关的抽象,从而实现从控制器代码自动生成、AI加速器代码自动生成、控制器和AI加速器数据搬运代码自动生成的功能;并且因为只需要维护一套和平台无关的高层次算子库(平台相关的内容自动由编译器产生),让算子库的维护变得更加简单。

兆松科技设计的这套“大编译器”在第一阶段支持基于RISC-V架构的AI芯片(包括数据流芯片),未来会逐步扩展支持非RISC-V架构的AI芯片。

本次演讲主要分享兆松科技是如何通过“大编译器”来解决AI模型到异构系统端到端高效适配的问题。

三、三类门票支持购票 免费票请注意查收

本次峰会设有四类电子门票,分别为免费票、免审票、通票和贵宾票。其中,免费票,申请后需经主办方审核通过方可参会,免审票、通票和贵宾票均需购买。

免费票、免审票可参加主会议及中国RISC-V计算芯片创新论坛。对Chiplet关键技术论坛和智算集群技术论坛感兴趣的朋友,可以选择通票或贵宾票购买后参会。

大家可以扫描下方二维码,添加小助手“雪梨”即可进行免费票申请,或购买电子门票。已添加过“雪梨”的老朋友,给“雪梨”私信,发送“GACS24”即可。

此前已申请免费票的朋友,组委会的审核和通知工作正在进行中,小助手会对通过审核的朋友进行微信告知(优先微信,并辅以短信或电话),请您查收和回复。