台积电 2nm 工艺被苹果独占,先进制程之路不停歇

没有竞争对手,台积电又要抢跑埃米工艺。

今年5月,苹果COO杰夫·威廉姆斯(Jeff )曾低调拜访台积电,台积电总裁魏哲家亲自接待。

距外媒报道,Jeff此行目标只为一件事:那就是确保苹果的2nm产能。

在AI竞赛下,台积电的产能实在是抢手,英伟达、博通、高通等科技巨头都是台积电的大客户。

不过从供应链透露的情况来看,2nm因为太先进且太贵,在很长一段时间里都会被苹果独占。

此外,由于成本预估过高,苹果预计到2026年才会在 Pro系列上采用2nm芯片。

虽然芯片进程迭代的周期被拉长,但在追求先进制程的道路上,台积电并没有放缓步伐。

在年初公布1.6nm(TSMC A16TM)半导体工艺后,该技术在近期有了重大突破。

新思科技()本周披露了一项针对于1.6nm工艺的背面电源布线项目,将对万亿晶体管芯片的设计至关重要。

虽然1.6nm在名字上还被叫做“纳米”,但台积电将其命名为A16,即16埃米。

埃米是比纳米还小一级的单位,因此16埃米在等价成1.6纳米后,在技术难度上其实提高了不仅一个量级。

据今年台积电发布会上公开的资料,TSMC A16TM技术将采用领先的纳米片晶体管,并结合创新的背侧电源轨方案,计划于2026年投入生产。

背侧电源轨方案是一种晶背供电的逻辑IC布线方案,该技术可以分离电源线与讯号线的配置,推动2nm以下逻辑芯片持续微缩,还能增强供电效能从而提升系统性能。

我们用大白话解释一下,那就是晶圆背面的空间很有利用的发展潜力,如果能将电源轨从前端移到背面,那么可以缓解晶圆正面的拥塞,自然就能实现芯片的微缩,这就是A16TM技术的思路之一。

据估算,相比于苹果采用的N2P工艺,A16TM技术能在相同的Vdd(正电源电压)下提供8-10%的速度提升,并在相同速度下降低15-20%的功率消耗,最终实现最高达1.1倍的芯片密度提升。

当然,想法很好,如何设计就是下一步的难题。

新思科技与台积电携手合作带来的背面电源布线技术,共同推动万亿晶体管级别的AI和多模芯片设计。

另外,台积电还与另一家软件公司ANSYS展开深度合作,双方将整合AI技术,以加速3D集成电路的设计进程。

值得一提的是,新思科技在今年年初达成协议,将花费350亿美元收购仿真软件巨头Ansys,但这项交易在今年8月遭到英国的反垄断审查,并有可能被其他国家监管机构调查。

在各方交易仍处在变数的情况下,台积电与两家公司的合作也算是给EDA行业带来一种积极的信号。

回到A16TM技术,台积电高管在会上表示,人工智能芯片公司可能会成为这项技术的首批采用者,而不是智能手机制造商。

目前已知首颗芯片将采用该技术,专为Sora定制, CEO奥特曼甚至打算募集7万亿美元与台积电合建晶圆厂以促进自研芯片进度,但很长一段时间里都没有进展。

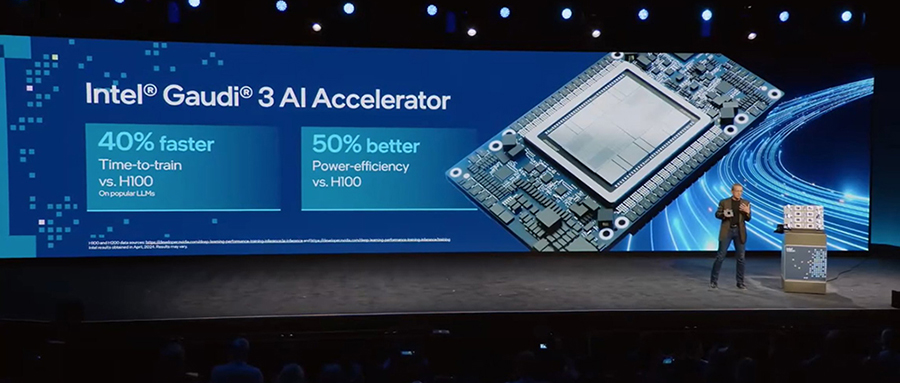

另外还有一个重要信号,那就是与台积电竞争埃米节点的英特尔在最近负面消息频出,甚至传出将售卖欧洲总部大楼以换取资金。

可以说,在英特尔解决自身危机之前,台积电在埃米节点已经一骑绝尘,此时透露最新进度,言外之意就是告诉大客户:打钱!

本文来自微信公众号“镁客网”,作者:jh,36氪经授权发布。