IC China 2024 开幕,AI 与半导体互为推动,引发新一轮科技革命

飞象网讯(源初/文)第二十一届中国国际半导体博览会(IC China 2024)在北京国家会议中心开幕。会上,当嘉宾们谈到半导体行业的发展时,AI已经成为了一个绕不开的话题,它因半导体而获得了算力,算力的猛增又拉动了新的需求。然而,面对复杂的行业外因素,如何寻找突破口也同样是备受关注的话题。

AI与半导体互为推动

AI正在引发新一轮科技革命,从语言模型、多模态模型的单体智能,到能够使用思维链(CoT, Chain of )进行推理的,再到使用工具完成复杂任务的智能体(),AI基础能力正在快速演进。AlI将成为智能时代的基础设施,融入生产和生活的每个环节,重塑千行百业,引发新一轮科技和产业革命。

AI与半导体已经形成了一种相互促进的关系,共同推动下一轮技术超级周期的到来。

首先,半导体技术为更多的应用场景提供了支持,包括人工智能(AI)、物联网(IoT)、5G通信和数据中心。这些应用反过来又产生了海量数据,为AI的深度学习模型提供了驱动力。一项基于亚洲的数据显示,自2019年以来,AI、物联网和汽车等领域的数据量呈现出71%的年均复合增长率,反映出技术快速演进和广泛的市场需求。

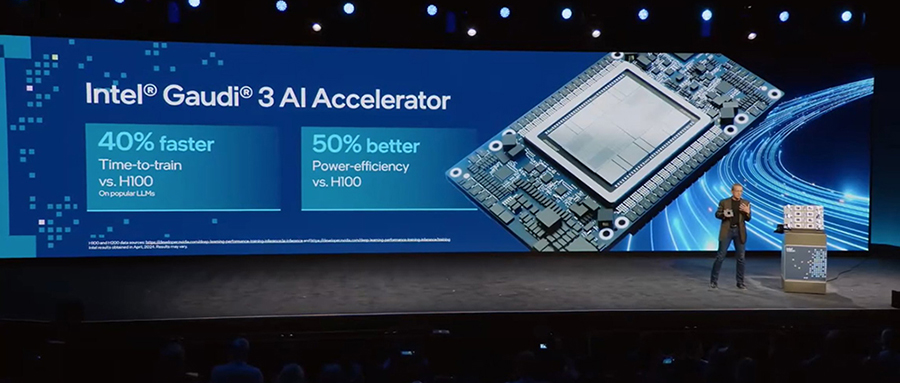

此外,大数据正被称为“新的石油”,推动了AI算法和半导体行业的发展,特别是在AI加速器、高带宽内存(HBM)、存储和网络等关键领域。随着AI技术的进步和大规模应用,半导体将进一步推动这些技术落地,形成互为推动的良性循环。

巴西半导体行业协会机构主任罗萨娜·卡赛斯对于两者的话题也表示称,到2030年,仅AI一项预计将为全球经济贡献超过15万亿美元。半导体行业持续突破创新边界,研发更新、更强大的AI加速器。AI具备变革半导体设计和制造的能力。

与此同时,新兴技术的能耗问题引发关注。黄仁勋曾提到:“没有任何物理定律可以阻止AI数据中心扩展到一百万芯片,但其能源供应可能需要核电站。”AI与人脑比较而言,人类大脑的功耗不超过25W,而英伟达8卡功耗达14.3kW。考虑冷却系统耗电量,百万卡智算中心能耗将高达3GW。会上,有位嘉宾还做了这样的比较,在京沪高铁线上的每位乘客耗电量约为30度电,而预计全球数据中心在2024年的总耗电量将达7000亿度。

AIDC在支持AI技术高速发展的过程中,逐渐呈现出高频宽、大容量、大能耗三大趋势。首先,AI模型的发展需要处理海量数据,这对数据中心的计算与传输能力提出了更高要求;其次,AI的快速进步导致模型和数据规模显著扩张,推动了存储和处理能力的跃升。最后,随着算力和存储需求的快速增长,AIDC的能耗问题愈发突出,已成为行业的重要挑战。

面对市场的机遇与挑战,寻找行业突破口自然也就成为大家关注的话题。

行业突破口在何方

对于国内产业而言,会上有嘉宾表示,应当重视系统和芯片架构创新,缩小技术差距。应当积极开展芯片架构创新,如采用3D堆叠//存算一体等新架构,努力缩小大算力芯片的技术代差。积极开展异构大算力集群系统的架构和任务调配等方面的优化工作,努力缩小大算力集群系统的性能差距。

同时,还要重视端侧AI技术创新,端侧AI拥有清晰的商业模式,更易实现规模化落地。其芯片对算力(如TOPS数量)和制造工艺(如7nm及以上工艺)的要求相对较低,从而降低了研发和生产成本,为更多企业参与创造了机会。此外,端侧AI应用场景多样化,包括智能设备、车载终端和工业物联网等领域,这些需求驱动了端侧AI的快速发展。面向半导体行业,需要探索多核异构计算架构,提升端侧设备的算力效率与适配能力。开发兼容多种终端应用的AI软件堆栈,以及高效的端侧芯片。端侧AI的未来将以低成本、高效能和广泛应用为目标,推动人工智能在终端设备上的深度集成与创新,构建更加智能化的生活与产业生态。

面对先进制程所带来的成本与制造上的压力,正在成为一种毋庸置疑的发展趋势。原有情况下,系统级芯片SoC( Chip)将不同功能元器件整合在单个芯片上,开发时间长、良率低,且各功能模块的纳米制程必须相同,都得用5oC上要求最高模块的制程,成本较高。

系统级封装SiP( in a )将多芯片异构集成,开发时间较短、良率较高,部分可重复使用。一个系统中,芯片往往只占系统中器件数目的10%左右。如果把其他所有器件都集成在单一芯片上,可能会导致性能不佳,成本增加。

对需要实现的复杂功能进行分解,然后开发出多种具有单一特定功能的裸芯片,这些来自不同功能、不同工艺节点的裸芯片可相互进行模块化组装,最终形成一个完整的芯片。这种方法实现了异质集成,为芯片设计带来了更大的灵活性和可扩展性,有效提升了产品的功能性。例如图上左边的SOC上所有模块都需要用同一制程(例如按CPU、GPU要求用7nm),整体成本较高,而右边的上各模块分别采用了7nm、14nm、22nm、28nm等多种制程,整体成本较低。

具备良率、成本、异构计算等优势,适用于复杂功能的定制化需求。由于由多颗芯粒组成,单颗芯粒的面积较小,其良率高。直接设计一整块SoC的面积较大,可能导致较低的良率,从而带来高昂的成本。此外,技术支持封装内部的异构集成,可以根据模块功能选择芯片制程,针对特定功能模块设计专用的高性能芯片,对于其他通用芯片粒采用成熟制程,从而降低成本。

DSA架构为发展智能计算算力提供新途径。当前智算的发展对计算架构提出了新的要求和挑战,包括更高的性能、更低的功耗、更强的并行计算能力和更好的安全保障能力等等。这些年软件定制化已经普遍采用,但硬件定制化仍有待于解决,基于RISC-V的DSA可能在这两方面提供了一条新途径。

RISC-V在设计思想中就包含了DSA的概念。为此,RISC-V架构包含了模块化和自定义扩展指令集功能,并为扩展指令集预留了很大的扩展空间。这样,用户可以为某个新应用或某个新算子,自定义一套扩展指令集及其支持硬件模块,容易构成一个高效的DSA系统。

DSA面向特定领域,通过定制的架构以更好地适应需求,例如用于机器学习的神经网络处理器,用于图形学、VR等的GPU,可编程网关和接口。DSA需融合硬件和软件技术,包括:更有效的并行算法,更有效的存储带宽利用,削减不必要的计算精度,采用面向领域的编程语言DSL。DSA可与面向领域的语言DSL相结合,如、。发展DSA需要新的技术队伍,他们了解并掌握垂直集成的一系列技术,包括特定领域的应用,适合该领域的DSL和相关的编译技术,架构原理,实现技术等等。

AI与半导体正共同推动全球科技与产业变革。AI对算力需求的增长反向驱动半导体技术创新,如和DSA架构降低成本并提升性能,同时端侧AI以低功耗、高效能的特性成为商业化重点方向。未来,行业需聚焦芯片架构优化、异构计算能力提升,以及开放标准与软硬件协同,加速低功耗技术研发,解决能耗瓶颈。在这一良性循环中,AI与半导体将共同引领智能时代的技术革命与产业升级。