台积电:从垂直整合到横向分工,成为半导体行业幕后推手

如今,横向分工已经司空见惯,半导体由AMD、苹果、、高通等设计和销售,制造则由台积电、三星等代工厂负责,但台积电1987年成立时,垂直整合,其中半导体制造商拥有自己的工厂,从设计、制造到销售,一手包办,这是司空见惯的事情。

从那时起已经过去了近40年,而现在,除了英特尔等一些例外,情况已经完全改变,台积电拥有全球一半以上的市场份额,现在可以称为半导体行业的幕后推手。

台积电日本有限公司代表董事社长小野寺诚先生向大家介绍了台积电在日本的概况。 “日本台积电持续增长,1997年达到1.5亿美元,2010年达到6亿美元,2023年达到41亿美元。一年前,我解释说这个数字是38亿美元,因此,我们继续看到正增长。特别是2023年,台积电全球出现7%到8%的负增长,而日本则出现正增长。”

对于我们2023年的业绩,小野寺先生表示,“12英寸等效晶圆数量为1,489,000片,接近150万片,自1997年以来累计总数已超过1000万片。我在日本的业务进展顺利,他解释道。

日本办事处方面,除了横滨总部以外,我们还在茨城县筑波市设有3DIC研究中心,在大阪和横滨设有日本设计中心,为采用尖端工艺节点的产品开发提供支持。此外,今年(2024年)2月举行的JASM(日本先进半导体制造)工厂是台积电在日本熊本县开设的第一家工厂,准备工作进展顺利,旨在开始量产。

该工厂是一家使用28nm至12nm等已经成熟的工艺节点(制造技术)制造半导体的半导体工厂,主要用于日本等市场的主要需求的CMOS逻辑半导体和汽车用微控制器。

先生表示,“针对7nm等更先进工艺节点的第二阶段项目已经开始”,台积电在日本的业务将基于JASM继续扩大,这是预期的情况。

兼容的N2将于明年发布,背面供电的A16将于2026年底量产

台积电高级副总裁兼副联席首席运营官 Kevin Jiang 概述了该公司在日本技术研讨会上的内容。

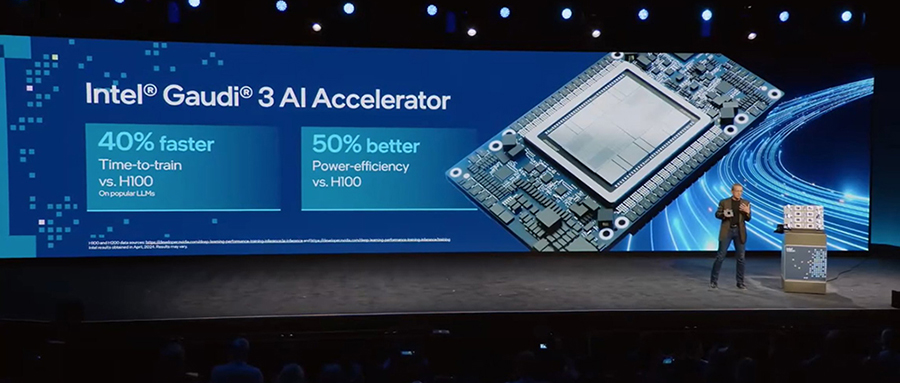

“目前,由于人工智能,对计算性能的需求确实呈爆炸性增长。例如,在我们的客户 ,V100 上 FP16 的性能为 ,但 H100 上 FP8 的性能已提高到 4,,甚至更进一步今年发布的 FP4拥有20,000 ,晶体管数量从V100的210亿个晶体管增加到2080亿个晶体管,增加了近10倍。”实现这一需求的半导体工艺节点和后工艺(等)变得重要。为此,台积电的半导体研究人员数量逐年增加,到2023年将达到9149人,用于研发的成本预计将增至58.46亿美元。

在向工艺节点演进方面,包括3nm(N3节点)在内的各工艺节点的开发进展顺利。 N3已于去年(2023年)开始量产,目前正在开发N3E、N3P、N3X等版本,N3E预计于今年开始量产。

除了用于制造苹果的 A17 Pro 之外,N3 还被透露用于制造英特尔计划在第三季度推出的 Lunar Lake 计算模块,它已成为很可能在多种产品中采用的工艺节点。

2025年将推出2nm(N2),N2将推出一种名为的技术,该技术调整了称为GAA(Gate All )的4D形状FET的配置。这使得优化裸片尺寸、性能、功耗等成为可能,称为 PPA(单位面积性能和功耗的缩写)。

此外,量产计划于 2026 年底开始,推出名为 A16 的工艺节点,该节点的尺寸从纳米到埃更小。 A16一代将引入一种称为超级电源轨(SPR)的“背面供电技术”,通过在硅背面提供电源层来改善整个硅的电气特性。芯片正面的信号质量和时钟频率供应质量可以得到改善,而背面的电源层的电源质量也可以得到改善。

与 N2 的 N2P 变体相比,A16 在相同电源下性能提升 8-10%,在相同性能下功耗降低 15-20%,裸片密度解释为 1.1倍。

通过开发 CoWoS 和 SoIC 等 2D 和 3D 小芯片技术,支持 AI 半导体的发展

台积电方面表示,“随着制程节点的演进,后制程技术将在未来AI芯片的演进中变得重要”,并解释了台积电提供的2D和3D 技术。

事实上,目前提供的H100/H200使用台积电称为CoWoS的2D小芯片技术,在封装上实现HBM内存。此外,AMD的 /采用台积电的3D小芯片技术“SoIC”,在封装上嵌入内存和GPU芯片。

在 3 月份推出的 (B200/B100) 也将两颗 GPU 芯片和 HBM 内存混合在一个封装中。这样看来,目前用于AI的GPU无一例外地使用2D或3D ,很明显,将决定AI技术的未来。

在这些中,他特别解释了名为“3D OE”的技术,该技术将光通信引擎集成到子板、中介层等中。 2025 年,我们将首先推出一种名为 COUPE(紧凑型通用光子引擎)的技术,该技术使用 SoIC-X(SoIC 的一种变体)将 EIC 堆叠在 PIC 之上。

明年,即2026年,我们将能够使用CoWoS CPO技术将其集成到子板中,从而实现6.4Tbps的传输速度,同时将功耗降低一半,延迟降低至十分之一。除此之外,将CPO集成到包括CPU、GPU等在内的中介层中的技术将实现12.8Tbps的传输速度,进一步降低十分之一的功耗和5%的延迟。

现代超级计算机可以通过使用 、 等扩展 GPU,以及使用以太网、 等扩展 GPU,将多个 GPU 用作单个 GPU。 3D OE 等技术与流程节点的发展同样重要,因为它们可以在扩展过程中减少带宽和延迟,从而提高巨型 GPU 的整体性能。

他还解释了SoW(晶圆上系统)。目前,AMD正在使用台积电的3D小芯片技术,将用作高速缓存的SRAM以3D方向堆叠在芯片顶部。 SoW是该技术的高级版本,其中在制造晶圆的阶段就已经制造了多层,并且在制造过程中堆叠执行计算的逻辑电路和诸如HBM存储器的存储器,以增加存储器容量。

目前,汽车制造商 TESLA 推出的一款名为“Dojo”的人工智能学习芯片原型据说能够在晶圆上构建 5x5(即 25 个芯片)。

他还解释了“InFO-oS”和“CoWoS-R”是与汽车级兼容的技术,并表示使用3nm等尖端工艺节点构建强大芯片的环境已经具备。该公司呼吁集中在日本的汽车制造商和一级零部件制造商采用该技术。

参考链接